# Tigon/PCI Ethernet Controller

**Revision 1.04**

Alteon Networks, Inc. 6351 San Ignacio Avenue San Jose, CA 95119 (408) 360-5500

Part Number 020016

August 1997

$\ensuremath{\textcircled{}}$  1996, 1997, 1998, 1999 by Alteon Networks, Inc. All rights reserved.

#### Preface

Audience ix

#### 1 Introduction

PCI Local Bus11Performance11Flexibility11

#### 2 Architecture

Overview 13 15 **PCI Supported Features** PCI Bus Configuration 15 PCI Bus Arbitration 15 PCI Bus Transactions 15 **Read Operations** 15 Write Operations 16 **Termination Operations** 16 PCI Bus Interrupt 16 17 PCI Bus Errors PCI 64-bit Bus Extension 17 PCI 64-bit Addressing 17 Local Memory 18 Overview 18 Arbitration 18 Internal Processors 19 Events 20 Flash 20 Mailboxes 20 Host Buffer Descriptors 21 Gigabit Ethernet Buffer Descriptors 21 HOST DMA 22 22 Two Channels Endian Conversion 22 Buffer Alignment 22 Scatter/Gather 23 Gigabit Ethernet MAC 23

#### **3 Internal Processors**

Local Memory Map 25 Processor's Registers File 26 Instruction Set 26 **PRI** Instruction 29 JOFF Instruction 29 Instruction Cache 29 Data Cache 29 30 Multi-Processor Features Debugging Aids 31 Reset 31 Watchdog Timer 31 ROM Code 32 Bootload Data Structure 33 Accessing Serial EEPROM 33 Accessing Flash 33

#### **4 Internal Events**

Timer Event 35 Mailbox Events 35 UART Events 36 PCI Interrupt Event 36 **DMA** Completed Events 36 Assist Completed Events 36 DMA Read Attention 37 DMA Write Attention 37 Ethernet Transmit Event 37 Ethernet Receive Events 37 Ethernet Transmit Attention 37 37 Ethernet Receive Attention Software Events 38 Inter-Processor Events 38

#### **5 PCI Interface**

Target 39 32-bit Address 39 Synchronization 39 Burst Length 39 Wait States 39 Watchdog Feature 40 **Terminating Conditions** 40 Target-Abort 40 Disconnect 40 Retry 41 Master 41 Dual Channels 41 64-bit Addresses 41 Burst Length 41 Minimum Burst Length 42 Maximum Burst Length 42 Wait States 42 **Terminating Conditions** 42 Completion 42 Time-out 42 Master-Abort 43 Read Commands 43 Write Commands 43 44 Extensions 66 MHz PCI Clock 44 PCI ROM 44 Alternate PCI Commands 44 PCI Interrupt as an Input 45 Additional PCI Arbitration Output 45 Configuration 45 Access Methods 45 Preloading from Serial EEPROM 46

#### 6 Ethernet Transmit Interface

Transmit Descriptors 47 Transmit Descriptor Indexes 48 Transmit Descriptor Location 49 Transmit Buffer Indexes 49 49 Transmit Flow Control Transmit TAGs 50 Ethernet CRC Calculation 50 Generating CRC 51 Checking CRC 51

#### 7 Ethernet Receive Interface

Packet Structure 53 Errors 53 Receive Descriptors 54 Receive Descriptor Indexes 55 Receive Descriptor Location 56 Receive Buffer Indexes 56 Receive Flow Control 56

#### 8 DMA Assist

High and Low Priority Rings57DMA Descriptor Location57Combining DMA Descriptors58Descriptor Pointers58Long DMA Descriptor58Mini DMA Descriptor59

#### **9 Register Descriptions**

Host Register Access Methods 61 Shared-Memory Register Regions 61 Register Quick Reference 63 PCI Configuration Registers 66 Vendor ID 66 Device ID 67 Command 67 Status 68 Revision ID 68 68 Class Code Cache Line Size 69 Latency Timer 69 Header Type 69 BIST 69 Base Address Register 0 69 ROM Base Address Register 70 SubSystem ID 70 SubSystem Vendor ID 70 Interrupt Line 71 Interrupt Pin 71 Minimum Grant 71 Maximum Latency 71 **General Control Registers** 72

Miscellaneous Host Control 73 Miscellaneous Local Control 74 Miscellaneous Configuration 75 Timer 76 Timer Reference A/B 76 Semaphore A/B 76 PCI State 77 Main Event A/B 78 Mailbox Event A/B 79 Window Base Address 79 Window Data 80 Serial Data 80 Host DMA Registers 81 DMA Read Host Address 81 DMA Write Host Address 82 DMA Read State 82 **DMA Write State** 84 DMA Read Length 85 DMA Write Length 85 DMA Read Local Address 86 86 DMA Write Local Address DMA Read TCP/IP Checksum 86 DMA Write TCP/IP Checksum 87 Local Memory Configuration Registers 88 **Receive Buffer Base** 89 **Receive Buffer Producer** 89 Receive Buffer Consumer 89 **Receive Buffer Active Packet Start** 89 Transmit Buffer Base 90 Transmit Buffer Producer 90 Transmit Buffer Consumer 90 Transmit Next Packet Starting Address 90 **Receive Descriptor Producer** 90 Receive Descriptor Consumer 91 **Receive Descriptor Reference** 91 **CPU** Priority 91 **Transmit Descriptor Producer** 92 92 Transmit Descriptor Consumer Transmit Descriptor Reference 93 Transmit Next Descriptor Available 93 Host FIFO Access 94 Host DMA Assist Registers 95 Assist State 96 Assist Producer 97 Assist Consumer 97 Assist Reference 97 Read Channel High Next Descriptor Available 97 Write Channel High Next Descriptor Available 97 **CPU Registers** 98 CPU State 98 CPU Program Counter (PC) 99

CPU Hardware Breakpoint 99 CPU Instruction 100 CPU Adjust Stack 100 **CPU Internal SRAM Indirect Address** 100 CPU Internal SRAM Indirect Data 100 CPU Watchdog Clear 101 CPU General Purpose Registers 0-31 101 Ethernet MAC Registers 102 Ethernet Transmit State 103 Ethernet Transmit Auto-Negotiation 104 Ethernet MAC Address 104 Ethernet Transmit Random Backoff 104 Ethernet Transmit Lengths 105 Ethernet Thresholds 105 Ethernet Receive State 106 Ethernet Receive Auto-Negotiation 107 Ethernet Multicast Filter 107 Ethernet SERDES Configuration 107 Ethernet PCS Configuration 108 General Communications Region 109 CPU Page 0 109 Ethernet MAC Statistics 110 Mailbox 0-31 111 Software Defined Words 111 Local Memory Window 111

#### **10 Signal Descriptions**

PCI Interface113Local Memory Interface114Ethernet Interface115

#### 11 Timing

PCI Interface 119 Local Memory Interface 119 Transmit Ethernet Interface 120 Receive Ethernet Interface 120

#### 12 Package and Pinout

Package121Pinout121

#### Appendix A Tigon II (Revision 6) Errata

DMA 4 125 Summary: 125 Details: 125 Work-around Options: 125 MAC 6 127 Summary: 127 Details: 127 Work-around Options: 127 CPU 3 128 Summary: 128 Impact: 128

Details: 128 Work-around Options: 128

# Preface

### Audience

This document is intended for use by those considering and or implementing a Ethernet adapter card which is based on the Tigon PCI/Ethernet Controller. It is assumed that the reader has a basic understanding of the necessary issues related to the design of an adapter card, the PCI bus, as well as Ethernet signaling.

The following documentation should also be referenced:

#### **Documents**

PCI Local Bus Specification, Revision 2.1

PCI Special Interest Group P.O. Box 14070 Portland, Oregon 97214 (800) 433-5177

GigaBlaze<sup>™</sup> G10<sup>™</sup> Documentation Set, May 1997

LSI Logic Document DB14-000073-00

# 1 Introduction

### 1.1 PCI Local Bus

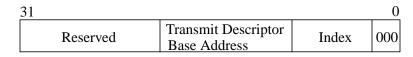

The PCI Local Bus is a high performance, synchronous bus, which is becoming widely accepted among system developers. The bus is capable of a maximum theoretical bandwidth of 528M Bytes per second when operating as a 64-bit bus at its maximum 66 MHz frequency. Provisions have been made to control latency at system configuration, thus allowing each machine to adjust to the flavor of adapters which have been installed.

The PCI Local Bus has also been optimized to allow direct interconnect between the bus connector and chips designed by vendors (i.e. no glue logic). The multiplexed address and data buses reduced the number of signals and pins associated with the PCI bus.

More information on the PCI Local Bus can be obtained by reading the "PCI Local Bus Specification" provided by the PCI Special Interest Group.

#### 1.2 Performance

Performance is essential for high speed networking adapters. Many aspects of the entire system need to be considered during the design process of such an adapter. The Tigon PCI/Ethernet Controller described by this document, was designed with the following key aspects in mind:

- Intelligence on adapter to offload host

- Reduce number of interrupts

- Reduce host accesses across PCI bus

- Reduce memory to memory host copies

- Low latency

- Checksum assist

- Hardware DMA channels

The combination of all of the above aspects has lead to the architecture of the Tigon chip, as well as the host driver which interacts with both the adapter and higher layers of software within the host.

### 1.3 Flexibility

The Tigon PCI/Ethernet Controller incorporates a philosophy of flexibility throughout the design. It was acknowledged that as hosts develop, and their software provides additional performance oriented features, the interaction with the adapter may need to change to take advantage of such features. This philosophy lead to a design in which the primary interaction between the host on the adapter is between two processors. The host being represented as one processor and the adapter containing another. This allows to generate software upgrades which enable new or unique features between the various host platforms.

#### Tigon/PCI Ethernet Controller

The software which runs on the Tigon's internal processor is referred to as firmware so as not to confuse it with the host driver. This firmware which interacts with the driver is actually contained within the driver and downloaded to the adapter during the initialization process. This prevents any issue of incompatible or outdated revisions between the host driver and the firmware. This also adds to the ease of installation of new software. No special firmware loading utility or PROM swapping is required.

Since the PCI Local bus is a relatively simple handshake, it is possible to create PCI to other bus bridges. These bridges can be used in conjunction with the Tigon to provide connectivity to other standard buses, or to proprietary higher bandwidth internal buses of a host.

Finally, even the Tigon itself was built around the concept of building blocks. The various interfaces provided by the chip as well as the internal processor are virtually independent objects which can be replaced or upgraded in future versions of the chip. This allows the possibility, for example, of a new chip which keeps the same host interaction, but uses a different bus interface. The internal processor could be expanded to become more powerful. Even the Ethernet interfaces can be replaced with other network interfaces.

### 2.1 Overview

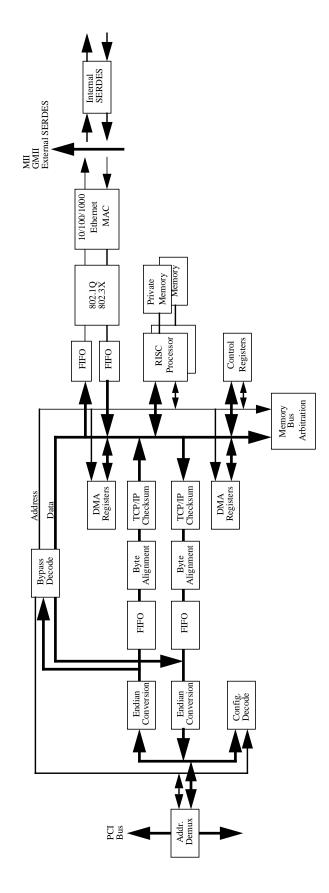

The Tigon PCI/Gigabit Ethernet Controller is designed to be a high integration and high performance Gigabit Ethernet ASIC used in adapters for workstations and personal computers. This ASIC is compliant with the PCI Local Bus Specification Revision 2.1. The Tigon contains the DMA functions necessary to off load either the host or the adapter from having to move data between the different memory spaces. A block diagram of the Tigon chip is shown on the next page.

As data is transferred between the two interfaces it is buffered in a FIFO. This allows for buffering and proper synchronization of the data to the output interface. Internally there are two FIFOs, one dedicated to each direction.

The design fully supports automatic handling of misaligned buffer transfers. This means that the data to be moved can be transferred between any two buffers regardless of the alignment of either buffer. For implementations which support the ability to DMA the data directly into the application's memory space, this feature might prevent the host from having to make unnecessary data copies. Internally, data is aligned to the FIFO boundaries.

A TCP/IP style checksum is calculated on all data that is transferred through the Tigon FIFOs. Any implementation in which the host supports hardware checksum assist can benefit from this hardware calculation. The checksum is calculated and automatically stored for each DMA buffer descriptor.

The PCI specification is inherently little-endian. Not all hosts want the data presented in the little-endian format. The Tigon contains the ability to do little-endian to big-endian swaps on either 8 byte or 4 byte boundaries. It is also possible that the Tigon can be used as a basis for non-PCI interfaces which expect the data to be in a big-endian format. This feature allows for the maximum flexibility.

The Tigon also contains a processor to manage the reading and chaining between buffer descriptors. Buffers can be chained to support the "scatter/gather" model of host memory. The code for this processor can be modified in order to optimize the format of the buffer descriptors to that which is most efficient for the host.

Figure 1. Tigon PCI/Gigabit Ethernet Controller Block Diagram

# 2.2 PCI Supported Features

#### 2.2.1 PCI Bus Configuration

The PCI specification provides a mechanism for adapters to be uniquely configured depending on the resources available in the host in which they are inserted. In the personal computer market this feature is called "Plug and Play." The Tigon fully supports this configuration process.

At the heart of the configuration process is a maximum 256 byte region in which the adapter's PCI interface can be controlled. The adapter uniquely identifies itself and indicates to the host what it requires in terms of memory space, I/O space, bus latency, interrupts, etc. The host in return provides the adapter with the necessary information. The can host also build a data structure in its own memory which software can use to determine what adapters are in the system.

In order to simplify the Tigon PCI/Gigabit Ethernet Controller, only configuration registers are controlled by the PCI clock while all other registers are controlled by the Memory Bus clock. This enables all non-configuration registers to be accessed even if the PCI clock is not present. The actual description of these registers for the Tigon PCI/Gigabit Ethernet Controller are contained in the "Register Descriptions" chapter.

All supported configuration registers are preloaded after a reset from the serial EEPROM. This preserves the adapter configuration information even if the adapter it is moved between machines. When necessary, software can update the contents of the EEPROM if the configuration needs to be altered.

#### 2.2.2 PCI Bus Arbitration

Since the Tigon is capable of being a PCI bus master, it participates in the bus arbitration process. The mechanism for this arbitration is outlined in the PCI specification and will not be repeated here.

The ability to arbitrate for the PCI bus and become a bus master is not enabled until the adapter is fully configured. This, however, does not prevent slave operations from accessing the Tigon. Once bus mastering is enabled it is important to note that the Tigon has no control over the arbitration algorithm used by the host. The PCI specification indicates that this is host specific.

#### 2.2.3 PCI Bus Transactions

#### 2.2.3.1 Read Operations

The following read operations are supported by the Tigon PCI/Gigabit Ethernet Controller:

| Command Description  |                                                                        | as Target | as Master |  |

|----------------------|------------------------------------------------------------------------|-----------|-----------|--|

| Configuration Read   | Read to Configuration region                                           | Yes       | Yes       |  |

| Memory Read          | Read of 2 or less words                                                | Yes       | Yes       |  |

| Memory Read Line     | Read of 3-12 words;YesYesor > 1/2 cache line if cache size enabled     |           |           |  |

| Memory Read Multiple | Read of more than 12 words;<br>or > 1 cache line if cache size enabled | Yes       | Yes       |  |

#### Table 1. PCI Read Operations

#### 2.2.3.2 Write Operations

The following write operations are supported by the Tigon PCI/Gigabit Ethernet Controller:

| Command                 | Description                         | as Target | as Master |  |

|-------------------------|-------------------------------------|-----------|-----------|--|

| Configuration Write     | Write to Configuration region       | Yes       | Yes       |  |

| Memory Write            | Write to Memory region              | Yes       | Yes       |  |

| Memory Write Invalidate | Write a cache line to Memory region | Yes       | Yes       |  |

#### Table 2. PCI Write Operations

#### 2.2.3.3 Termination Operations

An operation on the PCI Bus may be terminated for any of several reasons. The Tigon PCI/ Gigabit Ethernet Controller responds to all of the following termination methods described in the PCI specification.

| Table 3. | PCI Termination Operations |

|----------|----------------------------|

|----------|----------------------------|

| Termination Method | Description                                 |  |  |  |

|--------------------|---------------------------------------------|--|--|--|

| Normal Completion  | Master concluded its intended transaction   |  |  |  |

| Master Time-out    | Grant was removed and latency timer expired |  |  |  |

| Master Abort       | No target responded                         |  |  |  |

| Target Retry       | Unable to process transaction now           |  |  |  |

| Target Disconnect  | Unable to respond within latency guidelines |  |  |  |

| Target Abort       | Target will never be able to respond        |  |  |  |

As a target, the Tigon will never generate any of the three possible termination methods. All target operation must be terminated by the master.

#### 2.2.4 PCI Bus Interrupt

The PCI specification allows for up to four interrupts to be used by an adapter. If an adapter uses more than one, then it must have a separate function for each interrupt. Since the Tigon PCI/ Gigabit Ethernet Controller is a single-function device it only supports one interrupt. This single interrupt should be connected to the INTA# signal on the PCI Bus.

**NOTE:** Some computers require interrupts to be shared with other devices, it it is left to the driver to determines if interrupts are being shared.

All PCI interrupts are "level sensitive," and are considered asserted when low. Since interrupts may be shared, they are required to use open drain output drivers.

### 2.2.5 PCI Bus Errors

There are two possible types of errors defined by the PCI specification, parity errors and system errors The Tigon PCI/Gigabit Ethernet Controller supports both of the error reporting mechanisms.

Parity errors are checked across the data bus by the receiving agent on the PCI Bus during all transactions except during a Special Cycle command. Therefore only one PCI Bus interface can drive the parity error signal at a time. This active low signal is driven by a tri-state driver which must drive the signal high again before going tri-state. This signal is synchronous to the PCI clock.

System errors are checked across the address bus and also the data bus on a Special Cycle command. Any interface on the PCI Bus can indicate a system error. This active low signal is driven by open drain drivers and utilizes a weak pull-up on the host to become deasserted. The assertion of this signal is synchronous to the PCI clock, but the deassertion should be considered asynchronous.

#### 2.2.6 PCI 64-bit Bus Extension

The PCI specification supports a 64-bit data path in addition to the standard 32-bit data path. A total of 39 additional signals are used to provide this functionality. This extends the maximum bus bandwidth from 132 MBytes/second to 264 MBytes/second.

It is important to note that the PCI specification allows 64-bit operations with memory commands but they are not allowed for either I/O or Configuration commands.

The Tigon provides a 32/64-bit PCI interface. A protocol is defined by the PCI specification to determine what data width the host supports. Since the Tigon internally utilizes a 64-bit datapath, it was natural to build in the support for either PCI bus width.

### 2.2.7 PCI 64-bit Addressing

The Tigon PCI/Gigabit Ethernet Controller supports the full 64-bit addressing only as a bus master. However, the memory region required by the Tigon must be mapped into the 32-bit memory space. This implies that hosts which use 64-bit addressing must map the Tigon's memory region into the lower 4 GBytes of memory.

If utilized, the 64-bit addresses are indicated by the Tigon on the PCI bus through the use of Dual Address Cycles (DAC). The PCI specification indicates that devices capable of driving 64-bit addresses must signal a Single Address Cycle (SAC) when the upper 32-bits are all zeros in order to communicate with devices which use 32-bit addresses. This SAC technique is used by the host to access the Tigon's memory region.

# 2.3 Local Memory

#### 2.3.1 Overview

The Tigon PCI/Gigabit Ethernet Controller provides a 64-bit high-speed memory bus to connect to local memory. The internal data structure of the Tigon is built around this 64-bit bus width.

The maximum frequency of the Memory Bus is 50 MHz. This allows for a maximum bandwidth of 800 MBytes/second with synchronous memory and 400 MBytes/second with asynchronous memory. Each access into the SRAM located on the Memory Bus can be to any address. Therefore no bursting is required by this memory design. The same clock which controls the local memory is used to control the majority of the Tigon chip; it is considered asynchronous from the PCI Bus clock.

Any combination of byte, half-word, or word writes are allowed by the hardware. Reads always supply 64-bits of data from the external memory. The memory sub-system has no knowledge as to whether the useful portion of the data is a byte, word, etc.

#### 2.3.2 Arbitration

There are six possible entities within the Tigon which arbitrate for the use of the Memory Bus. A priority scheme is enforced between these six requesters so that no requester can cause a loss or corruption of the dataflow.

Table 4 lists the possible sources which can request a memory operation. A relative priority between these sources is also noted. This priority is not necessarily absolute and is discussed after the figure.

| Access Source             | Relative Priority        |

|---------------------------|--------------------------|

| Gigabit Ethernet Transmit | 1                        |

| Gigabit Ethernet Receive  | 2                        |

| Host Slave Access         | 3                        |

| DMA Assist                | 4                        |

| PCI Read DMA              | 5                        |

| PCI Write DMA             | 5                        |

| Internal Processors       | 6<br>(3 if waiting long) |

|  | Table 4. | Local | Memory | <b>Priorities</b> |

|--|----------|-------|--------|-------------------|

|--|----------|-------|--------|-------------------|

The two Gigabit Ethernet interfaces have the highest priority within the Tigon. It is imperative that the Gigabit Ethernet interfaces never underrun or overrun. Each of the Gigabit Ethernet interfaces requires attention on average every 128ns.

Host accesses to the Tigon's target logic must occur in a timely fashion and therefore it is next in the priority scheme. Such a host access indicates that there is currently no DMA activity on the bus. Depending on the level of Gigabit Ethernet activity a host access is serviced between 1 and 5 internal clock cycles.

The two PCI DMA engines alternate priority depending on which one is actively on the PCI bus. It is expected that the sustainable host memory access bandwidth will vary greatly between different host PCI interface designs. In an environment with bi-directional Gigabit Ethernet traffic, it is expected that the two DMA engines will alternate access to the host memory.

If an asynchronous local memory is used, the default priority of the internal processors can be altered via a configuration register. Normally it is considered lowest priority as long as all the other higher priority data transfers are in progress. Since the primary job of the processor is to keep the data moving, it's job is most critical when there is data to be moved which hasn't yet started. As long as any one of either Gigabit Ethernet or the PCI DMA is not active, then there will be sufficient bandwidth for the processors. Each processor is not starved for memory bandwidth since it has an instruction cache as well as a mechanism to advance to the third priority if it's request has been waiting too long.

If a synchronous local memory is used, the two processors would alternate with each other just below the DMA priority. The default priority register for each processor is ignored. To improve local memory utilization the Gigabit Ethernet, DMA channels, and CPU instruction fetch interfaces will all perform several back-to-back operations for each arbitration cycle.

# 2.4 Internal Processors

The Tigon PCI/Gigabit Ethernet Controller contains one or two embedded 32-bit processors depending on the revision of the Tigon. The processors can be used for any function including parsing buffer descriptors and controling the DMA hardware registers. These processors can be set up to accommodate different buffer descriptor formats, allowing the Tigon chip to adapt to the communication method which best suits the host. This approach is consistent with the goal of providing a flexible PCI Controller solution.

Fully contained inside the Tigon, the processors are capable of generating operations to the PCI Bus as well as to local memory. This allows control information to be located in either memory space. All registers internal to the Tigon can also accessed by either the embedded processors or the by the host through the Tigon's target interface.

The operation of the processors is governed by firmware. External to the Tigon will be a small non-volatile serial EEPROM which will contain all the power-on diagnostics and PCI initialization tasks. Any additional software can be downloaded by the host driver into the local SRAM memory. Since each local memory operation fetches 8 bytes, up to two processor instructions can be loaded into the Tigon on each instruction fetch cycle.

An instruction cache as well as internal SRAM is provided to enable the processor to not use any of the valuable local memory bandwidth for most firmware execution. The instruction decoding is modeled after the R4000 RISC processor with some instructions removed and several new ones added for embedded optimization.

Tigon revision 5 is the first revision to contain a second processor with its own internal SRAM. Each processor has full access to all functions within the Tigon. It is left to firmware to determine how best to utilize both processors. The model usually is either one processor manages each direction of traffic, or the one processor manages all traffic and the second processor adds higher level functions.

### 2.5 Events

The model with which the embedded processor executes is an Event model rather than an Interrupt model. This means that the processor is not interrupted from the task at hand, but each task should be kept to a small thread of code. There is significant hardware assist for event processing within the Tigon to facilitate a robust execution environment.

There is a single 32-bit register in the Tigon which includes bits for each of the events that the processor must handle. The processor's main loop is to wait for events and then deal with them in priority order. Two special instructions were created to allow the processor to index into an event handing jump table based on the most significant (highest priority) bit set in the event register.

Not all events are created by the hardware. There are several bits within the event register which are completely controlled by software. This allows software to queue events to be handled within the priority encoded main loop. The events in this register are described in the Register Descriptions Chapter.

One of the features that deserves special attention is the timer function. This is a 32-bit counter which advances every 1-128 local clock cycles based on a pre-scaler function. If the timer is set up to advance every microsecond, then the timer in effect rolls over every about every "70 minutes." A queue of time-based functions is maintained by the processor with the top entry in the queue managed by hardware. The processor can schedule future events by taking the current timer value and adding the number of "microseconds" at which it would like to receive an event. An event will be indicated by the hardware if the desired event time arrives or has passed within the last "minute." The processor makes heavy use of this event queue to provide time-outs, interrupts, and any other function in which it would be poor to just create a software spin loop.

### 2.6 Flash

The Tigon PCI/Gigabit Ethernet Controller has been designed to interface to an external flash for storage of important configuration and manufacturing information. All PCI adapters must provide configuration information to the host after power-up. The processor in the Tigon chip initially executes from this flash and loads all internal PCI registers from predetermined locations inside the flash after a reset. This enables the adapter to respond properly throughout the configuration process.

The flash technology allows vital adapter information to be accessed and updated whenever necessary. The host or local processor may read or write these locations via the Control Register. The two processors should not attempt to write the flash at the same time.

The flash has additional memory locations which are available for storage of non-PCI information. These locations can be used to store addresses, manufacturing data, diagnostic results, etc. Software is responsible for managing these locations.

### 2.7 Mailboxes

A common technique to facilitate communication between host processors and adapters, are mailboxes. Typically these are locations which are written by one processor which cause an interrupt to the other processor. The value written may or may not have any significance. The number of mailboxes in each direction is usually fixed. Each processor is allowed to read the mailbox only once before it is cleared by the hardware.

The Tigon has generalized the concept of mailboxes in order to provide greater flexibility in the interaction between the host and the adapter. In order to implement mailboxes in which the value of the mailbox is not significant, the processors need only define the software interrupts such that each interrupt has a predetermined meaning.

In order to implement mailboxes in which the value of the mailbox is significant, the adapter can map some of its local memory onto the PCI bus which functions as a mailbox window. This window is accessible by both processors and is predefined to be 1k bytes in size. The second 256 bytes of this window are divided into 32 8-byte locations and have a special meaning. A write to the upper half of any of these 32 locations will cause an event to the internal processor with a notification as to which location was written. Actually, there is a separate event bit for each of these 32 locations. The lower 256 bytes or the upper 512 bytes (i.e. not mailbox area) of this window have no predetermined meaning and can be software defined.

Software should be designed so that it is clear which processor is allowed to write to any given portion of the memory. This technique can be used to create many logical mailboxes of various size without being strictly limited by the hardware. An additional benefit to this technique is that the mailbox may be read as many times as necessary without the loss of the mailbox contents.

The first mailbox has special meaning since the PCI interrupt pin is immediately deasserted when it is written. This feature allows software to define a mechanism for a host processor to clear the interrupt at the same time as passing a message to the Tigon's processor. If a hardware clear interrupt feature is not required in the software model, then this first mailbox need not be utilized.

### 2.8 Host Buffer Descriptors

The main mechanism to effectively communicate between the host and the Tigon PCI/Gigabit Ethernet Controller is via buffer descriptors located in host memory. This is not the only technique as mailboxes are also supported. Host descriptors are efficient since they allow for larger amounts of data to be passed without the need for host access over the PCI bus. In most host environments each time the host processor directly accesses a location on the PCI bus, the host slows down and loses some of its processing time.

It is the responsibility of the Tigon's internal processor to use the DMA engines at its disposal to transfer the host buffer descriptors between host memory and its own local memory space. These host buffer descriptors have no correlation to the registers used to control the DMA engines. These descriptors are a software convention for communication between the host processor and the Tigon processor and are not fixed by the hardware.

The document entitled "Gigabit Ethernet/PCI Network Interface Card Host/NIC Software Interface Definition" details how the host communicates to the Tigon.

# 2.9 Gigabit Ethernet Buffer Descriptors

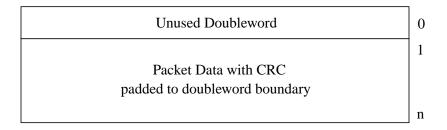

The only mechanism to queue packets to and from the Serial Gigabit Ethernet transmit and receive interfaces, is through the use of Gigabit Ethernet Descriptors. These are fixed 8-byte structures which indicate to the Gigabit Ethernet state machines where the packets are located in the local memory.

For transmit packets, the descriptors contain the starting address and length of each packet. Special provisions are included to deal with packets up to 64k bytes. For more detailed information see the "Gigabit Ethernet Transmit Interface" chapter.

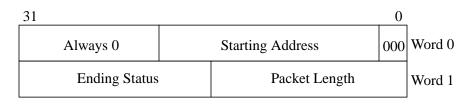

For receive packets the descriptors contain the starting address and length of the packet as well as indication of any unusual or error events detected during the reception of the packet. For more detailed information see the "Gigabit Ethernet Receive Interface" chapter.

# 2.10 HOST DMA

#### 2.10.1 Two Channels

The PCI interface within the Tigon PCI/Gigabit Ethernet Controller contains two independent DMA channels. One is used exclusively for host memory reads while the other is used exclusively for host memory writes. These DMA channels provide the only means by which the Tigon can access host memory.

It is the primary responsibility of the Tigon's internal processor to manage these DMA channels for the transfer of control information as well as network data. The maximum number of bytes the hardware can transfer in a single DMA operation is 64k bytes. Due to the typical memory paging schemes used by most host operating systems, these DMA channels are typically set up by the internal processor to DMA no more than a "page" worth of data. A new host address for the next page would be required after each DMA transfer.

### 2.10.2 Endian Conversion

There are two basic formats for storing data in memory. One is called Little-Endian, and the other is called Big-Endian. To facilitate communication between a host which has different endianness than the adapter, the Tigon PCI/Gigabit Ethernet Controller has included the necessary byte swapping support.

The PCI Bus is inherently little endian in nature since the configuration registers are defined to be little endian. The little endian format has the lower address contain the least significant part of the field. Since it is possible that not all hosts will adhere to the little endian format for regular data transfers, or that an adapter design may be big endian, this byte swapping feature is necessary.

All data going to or from the PCI Bus, except for the PCI configuration registers, can be swapped in groups of four or eight bytes. This byte swapping is individually selectable for each of the two DMA channels as well as for any host target accesses to the Tigon.

### 2.10.3 Buffer Alignment

Not all DMA transfers will be nicely aligned to 32/64-bit boundaries. In fact the data could be on any byte boundary. Traditionally many adapters have placed the burden on the host to align the buffers prior to data transfer. This is time consuming and ultimately hurts system performance. The Tigon PCI/Gigabit Ethernet Controller provides the necessary byte steering logic to compensate for misaligned buffers.

The Tigon includes the logic on the PCI side of the FIFO to compensate for the misalignment. Data from any host byte address can be aligned to any byte offset of the Tigon's internal memory. This flexible scheme allows multiple odd length, odd boundary buffers to be directly concatenated into the proper sequence prior to reaching the Ethernet MAC. This process also aids in the generation of the TCP/IP checksums.

At the beginning of all buffer transfers, the Tigon may need to move up to 7 bytes before it can begin regular full-speed bursting. The Tigon always bursts full words at a time into or out of the FIFOs. Similarly, at the end of a buffer transfer, there may be several leftover bytes which are transferred separately to complete the DMA operation.

#### 2.10.4 Scatter/Gather

The concept of scatter/gather is very much related to that of buffer descriptors and buffer alignment. The idea is that a portion of data to be moved is to be placed in several fragments throughout memory, or may already exist in several fragments. This required the DMA operation to either scatter or gather the data respectively during the DMA process. The ability to off load this responsibility from the host processor increases the host's efficiency and overall system performance.

The Tigon PCI/Gigabit Ethernet Controller has the necessary features required to efficiently support the scatter/gather process. First, buffer descriptors need to be built which indicate where buffers are and how much data is in each buffer. In the Tigon chip these descriptors are parsed by the internal processor which manages the DMA channels. Second, the buffers may not all be on the same alignment. Again the Tigon chip can automatically compensate for such misalignments.

# 2.11 Gigabit Ethernet MAC

Built into the Tigon is an Ethernet MAC capable of running at either 10/100/1000 Mbits/second. Support for 10/100 modes is achieved through an MII interface. Support for 1000 mode is currently done via external Fibre Channel components operating at Gigabit Ethernet speeds.

When utilized with an external serializer/deserializer (SERDES) chip, proper Gigabit Ethernet signaling is achieved. The Tigon provides the 62.5 MHz interface required by the SERDES. The SERDES takes care of converting this into the 1.25 GHz Gigabit Ethernet signals. This division allows the Tigon to be implemented in standard CMOS technology.

The transmit and receive Gigabit Ethernet interfaces function independent of each other when configured for full-duplex operation. The MAC is also capable of operating in half-duplex operation.

FIFOs are utilized between the internal clock domain and the 62.5 MHz interface to the SERDES in order to provide data synchronization. These FIFOs are as small as possible to conserve space inside the chip.

Hardware state machines manage the transfer of packets between the local memory and the Gigabit Ethernet interfaces. All packets are queued for transmission or reception through the use of Gigabit Ethernet Descriptors. The descriptors are directly referenced and updated by the hardware. This technique provides a mechanism for the internal processor to not have to support the hardware for each packet being transmitted or received.

The Tigon contains an internal 32-bit general purpose processor to control and manage the various DMA activities as well as to communicate with the host. This processor is a relatively independent block within the Tigon architecture. It was modeled after the R4000 RISC processor, however the supported instructions and their decoding is unique to the Tigon. Many instructions were removed and several new ones added for imbedded optimization.

The operation of the processor is governed by firmware. External to the Tigon will be a small non-volatile memory which will contain all the power on diagnostics and PCI initialization tasks. Any additional software can be downloaded by the host driver into the local memory SRAM. Since each local memory operation fetches 8 bytes, up to two processor instructions can be loaded into the Tigon on each instruction fetch cycle. A small instruction cache as well as SRAM internal to the Tigon (a.k.a Scratch Pad) is also provided to enable the processor to reduce its usage of the valuable local memory bandwidth. Firmware is compiled into the machine language opcode by using GNU R4000 tools.

Starting with Tigon revision 5, a second processor was added to the chip. To distinguish between the two processors the original one is called CPU A while the new processor is called CPU B. Both processors are equivalent with the exception that CPU B does not contain any ROM and CPU B contains less swatch pad memory than CPU A. A reset operation always halts CPU B.

### 3.1 Local Memory Map

The Local Memory Map defines which address ranges are to be used to access the external SRAM, external Flash, or internal Tigon registers. The local memory was implemented within a 32-bit address space. Table 5 indicates how this space was sub-divided. The regions define the maximum size provided, not all of the space need be occupied with valid locations. For example if only 256k Bytes of SRAM are assembled on the board, then only the first 256k Bytes in the External SRAM memory would be valid.

The Flash region allows for a 1M Byte of addressable space. This assumes that the full 8 byte datapath is utilized. Since most Flash implementations will use a single 8-bit wide device, the practical limit to the size of the Flash region would then become 128k Bytes.

| Address Range       | Access                                            | Max. Region Size |  |

|---------------------|---------------------------------------------------|------------------|--|

| 0x00000000-007FFFFF | External SRAM                                     | 8M Bytes*        |  |

| 0x00C00000-00C03FFF | Internal SRAM "Scratch Pad"                       | 16k Bytes†       |  |

| 0x40000000-400007FF | Internal Bootload ROM<br>(Instruction Fetch only) | 2k Bytes‡        |  |

| 0x80000000-807FFFFF | External Flash                                    | 8M Bytes*        |  |

| 0xC0000000-C00003FF | Tigon Registers                                   | 1k Bytes         |  |

Table 5. Local Memory Map

Tigon revision 4 has 2M byte limit.

† Tigon revision 4 has 2k bytes; Tigon revision 5 CPU A has 16k bytes and CPU B has 8k bytes.

CPU A only.

‡

# 3.2 Processor's Registers File

As with all processors, there are some register locations which are used only by the processor itself. These are not to be confused with the other Tigon registers which can be accessed also by the host. Architecturally there are provisions for 32 locations in this register file. Table 6 indicates the usage of these locations.

Table 6. Processor's Register File

| Register | Usage                            | Access |

|----------|----------------------------------|--------|

| rO       | Always contains 00000000h        | R/O    |

| r1-r31   | 32-bit general purpose registers | R/W    |

### 3.3 Instruction Set

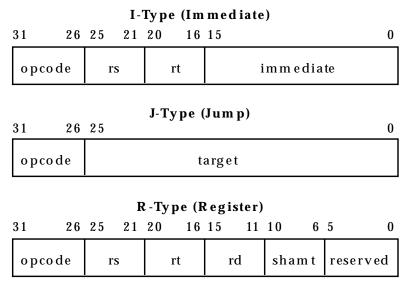

The executable instructions for the internal processor fall into one of three decoding formats. Instructions which require an offset or a 16-bit immediate field use the I-Type format. Instructions which don't use an immediate field or need to reference 3 registers use the R-Type format. Certain long jump instructions use the J-Type format. These three formats are shown in Figure 2.

Figure 2. Instruction Formats

Table 7 lists the basic instructions supported by the internal processor. A brief description of each instruction is provided. All opcodes which are not listed will cause the processor to immediately halt.

All instructions which are listed as *new* in the following table are R-Type instructions.

|                   | New          | Format | Opcode<br>[31:26] | REGIMM<br>[20:16] | SPECIAL<br>[5:0] | Description                      |

|-------------------|--------------|--------|-------------------|-------------------|------------------|----------------------------------|

| Load/Store        |              |        |                   |                   |                  |                                  |

| LB                |              | I-Type | 100000            | -                 | -                | Load byte                        |

| LBU               |              | I-Type | 100100            | -                 | -                | Load byte unsigned               |

| LH                |              | I-Type | 100001            | -                 | -                | Load halfword                    |

| LHU               |              | I-Type | 100101            | -                 | -                | Load halfword unsigned           |

| LW                |              | I-Type | 100011            | -                 | -                | Load word                        |

| LWL*              |              | I-Type | 100010            | -                 | -                | Load word Left                   |

| LWR*              |              | I-Type | 100110            | -                 | -                | Load word Right                  |

| SB                |              | I-Type | 101000            | -                 | -                | Store byte                       |

| SH                |              | I-Type | 101001            | -                 | -                | Store halfword                   |

| SW                |              | I-Type | 101011            | -                 | -                | Store word                       |

| SWL*              |              | I-Type | 101010            | -                 | -                | Store word Left                  |

| SWR*              |              | I-Type | 101110            | -                 | -                | Store word right                 |

| Arithmetic Imr    | nedia        | te     |                   |                   |                  |                                  |

| ADDI              |              | I-Type | 001000            | -                 | -                | Add immediate                    |

| ADDIU             |              | I-Type | 001001            | -                 | -                | Add immediate unsigned           |

| ANDI              |              | I-Type | 001100            | -                 | -                | AND immediate                    |

| ORI               |              | I-Type | 001101            | -                 | -                | OR immediate                     |

| XORI              |              | I-Type | 001110            | -                 | -                | XOR immediate                    |

| SLTI              |              | I-Type | 001010            | -                 | -                | Set less than immediate          |

| SLTIU             |              | I-Type | 001011            | -                 | -                | Set less than immediate unsigned |

| LUI               |              | I-Type | 001111            | -                 | -                | Load upper immediate             |

| Arithmetic        |              |        |                   |                   |                  |                                  |

| ADD               |              | R-Type | 000000            | -                 | 100000           | Add                              |

| ADDU              |              | R-Type | 000000            | -                 | 100001           | Add unsigned                     |

| SUB               |              | R-Type | 000000            | -                 | 100010           | Subtract                         |

| SUBU              |              | R-Type | 000000            | -                 | 100011           | Subtract unsigned                |

| AND               |              | R-Type | 000000            | -                 | 100100           | AND                              |

| OR                |              | R-Type | 000000            | -                 | 100101           | OR                               |

| NOR               |              | R-Type | 000000            | -                 | 100111           | NOR                              |

| XOR               |              | R-Type | 000000            | -                 | 100110           | XOR                              |

| SLT               |              | R-Type | 000000            | -                 | 101010           | Set less than                    |

| SLTU              |              | R-Type | 000000            | -                 | 101011           | Set less than unsigned           |

| PRI               | $\checkmark$ | R-Type | 000000            | -                 | 001011           | rd <- Priority Encode (rs & rt)  |

| Shift Instruction | ons          |        |                   |                   |                  |                                  |

| SLL               |              | R-Type | 000000            | -                 | 000000           | Shift left logical               |

| SRL               |              | R-Type | 000000            | -                 | 000010           | Shift right logical              |

#### Table 7. Internal Processor Instruction Set

| New               | Format     | Opcode  | REGIMM  | SPECIAL | Description                                                   |

|-------------------|------------|---------|---------|---------|---------------------------------------------------------------|

|                   |            | [31:26] | [20:16] | [5:0]   |                                                               |

| SRA               | R-Type     | 000000  | -       | 000011  | Shift right arithmetic                                        |

| SLLV              | R-Type     | 000000  | -       | 000100  | Shift left logical variable                                   |

| SRLV              | R-Type     | 000000  | -       | 000110  | Shift right logical variable                                  |

| SRAV              | R-Type     | 000000  | -       | 000111  | Shift right arithmetic variable                               |

| Jump and Branch I | nstruction | S       |         |         |                                                               |

| J                 | J-Type     | 000010  | -       | -       | Jump                                                          |

| JAL               | J-Type     | 000011  | -       | -       | Jump and link                                                 |

| JR                | R-Type     | 000000  | -       | 001000  | Jump register                                                 |

| JALR              | R-Type     | 000000  | -       | 001001  | Jump and link register                                        |

| JOFF √            | R-Type     | 000000  | -       | 001010  | PC <- (rs[20:3]   rt[12:0]) << 1                              |

| BEQ               | I-Type     | 000100  | -       | -       | Branch on equal                                               |

| BNE               | I-Type     | 000101  | -       | -       | Branch on not equal                                           |

| BLTZ              | I-Type     | 000001  | 00000   | -       | Branch on less than zero                                      |

| BLTZAL            | І-Туре     | 000001  | 10000   | -       | Branch on less than zero and link                             |

| BLEZ              | І-Туре     | 000110  | -       | -       | Branch on less than or equal to zero                          |

| BGTZ              | I-Type     | 000111  | -       | -       | Branch on greater than zero                                   |

| BGEZ              | I-Type     | 000001  | 00001   | -       | Branch on greater than or equa<br>to zero                     |

| BGEZAL            | I-Type     | 000001  | 10001   | -       | Branch on greater than or equa<br>to zero and link            |

| BEQL              | I-Type     | 010100  | -       | -       | Branch on equal likely                                        |

| BNEL              | I-Type     | 010101  | -       | -       | Branch on not equal likely                                    |

| BLTZL             | I-Type     | 000001  | 00010   | -       | Branch on less than zero likely                               |

| BLTZALL           | I-Type     | 000001  | 10010   | -       | Branch on less than zero and link likely                      |

| BLEZL             | I-Type     | 010110  | -       | -       | Branch on less than or equal to zero likely                   |

| BGTZL             | I-Type     | 010111  | -       | -       | Branch on greater than zero likely                            |

| BGEZL             | I-Type     | 000001  | 00011   | -       | Branch on greater than or equa<br>to zero likely              |

| BGEZALL           | I-Type     | 000001  | 10011   | -       | Branch on greater than or equa<br>to zero and link likely     |

| Miscellaneous     |            |         |         |         |                                                               |

| Halt / Break      | R-Type     | 000000  | -       | 001101  | Halt execution. A halt code car<br>be placed in bits [26:16]. |

### 3.4 PRI Instruction

The PRI instruction is most useful for creating an index into a jump table which is required by the JOFF instruction. The result of the PRI instruction is a value between 0 - 32 corresponding to the most significant bit number which was set after the two input parameters are ANDed together plus one. The ANDing allows for masking the input so that unwanted bit positions can be ignored.

# 3.5 JOFF Instruction

The JOFF instruction was created to facilitate quickly processing events through the use of a jump table. Generally the PRI instruction would be used first to create an index into a jump table. The JOFF utilizes the base address of a jump table along with an index to force the program counter into the proper place in the jump table. Each entry in the jump table is 8-bytes in length as it must consist of jump instruction followed by a jump delay slot instruction (i.e., usually a NOOP).

The jump table can be of any size, but must be placed in memory such that the base address of the jump table is aligned to a address boundary corresponding to the size of the jump table. For example, a jump table containing 16 entries occupies 128 bytes of memory and must be aligned to at least a 128 byte boundary.

The *rs* field in the instruction contains the jump tables' base in the form of a byte address. The *rt* field contains the index into the table (ex. normally 0-31). It is not expected that huge jump tables would really be used since the largest number the PRI instruction can generate is 31. Bits rs[20:3] and rt[12:0] are OR'd together prior to being shifted left 1-bit position. This final shift makes each jump table entry contain two instructions.

### 3.6 Instruction Cache

A small instruction cache was implemented to allow tight loops to execute without accessing external SRAM as well as to take advantage of the cache line fill feature which is inherent to many cache architectures. The instruction cache is organized as a single cache line which contains sixteen 32-bit instructions. The cache will attempt to fill the remainder of the cache line unless a branch instruction forces execution to a new location. External memory is organized 64-bits wide, therefore each instruction fetch operation to external memory will yield 2 instructions.

The internal processor is capable of sustaining one instruction per cycle as long as the instructions and any data loads have cache hits. Any time either cache has a miss, there is a minimum 3 or 4 cycle delay to fetch the desired data from the external asynchronous or synchronous SRAM respectively. The delay can be longer if there is contention for the SRAM from another source. This delay is usually experienced for instruction fetches each time the processor starts executing from a new cache line. Subsequent instruction fetches within the same cache line are usually cache hits since the cache quickly attempts to pre-load the remainder of the cache line.

# 3.7 Data Cache

The data cache was primarily implemented as a means to store the entire 64-bit value read from external memory during load instructions. Typically the processor will have data structures greater than 32-bits, therefore the reference to consecutive words will only create a single external memory operation. The data cache is organized as a single cache line which contains two 32-bit words.

A single write buffer was implemented so that the processor store instruction need not hold up the processor while it waits for completion. If a load or store instruction is executed while the write buffer is still full the processor will stall further instruction execution until the prior write completes. This ensures operations occur in the order executed.

Any time there is a data cache miss, there is a minimum 3 cycle delay to fetch the desired data from the external SRAM. The delay can be longer if there is contention for the SRAM from another source.

Bus snooping logic was also implemented to keep the integrity of the data cache even if another source writes to a location which is currently cached. During such an event the cache will be automatically updated with the new value. This means that any processor code which is looping waiting for an external memory location to be written will not actually be generating any external memory reads.

If the Tigon is configured for 1M Byte of SRAM, then the 1M-2M Byte address region is a repeat of the first 1M Byte of SRAM. In such a configuration the snooping logic will update the data cache during accesses to the same *repeated* memory region to keep it accurate with physical memory. In other words, even though reading address zero and 1MB will yield the same result, the snooping logic will only monitor the one region which was last used to fill the data cache line.

The registers internal to the Tigon but external to the processor are never cached. They always bypass the data cache without affecting the previous cache contents. There is a minimum 1 cycle delay when loading one of these type of register.

### 3.8 Multi-Processor Features

Since the Tigon revision 5 introduced a second processor, a few additional features were required to facilitate proper communication between the two processors. The details on how to enable each feature can be found in the register description chapter. This section is intended to provide an overview.

Since most firmware is driven by the main event register, a main event register for CPU B was added. All of the hardware events appear in both registers and it is assumed that firmware will mask the unwanted events. Each processor also has its own software event bits. Two software events bits from Tigon revision 4 where removed in order to add the ability for a processor to send an event to the remote processor, as well as for the local processor to be able to clear the remote processor's event.

All registers which support the debug of a processor have been duplicated for CPU B. In addition the Timer Reference register has also been duplicated allowing each processor to be able to generate its own time-based events. Each processor has its own scratch pad which appears in the same location for each processor (i.e. does not show up in the other processor's memory map and can only be accessed using the indirect debugging techniques).

The 32 mailboxes which the Tigon supports can be divided into two groups of 16 if both processors need access to mailboxes. The lower 16 are assigned to CPU A and the upper 16 are assigned to CPU B. This feature is enabled in the Misc. Local register. If only one processor needs mailboxes, then it can use the entire set of 32 mailboxes and it is assumed that the other processor would not reference the mailboxes out of convention.

To support usage of shared registers or memory locations, a hardware semaphore was created. If firmware needs more than one semaphore, then it is assumed firmware can create more using software techniques. The hardware semaphore utilizes two register decodes, one for each processor. For a processor to obtain the semaphore it must perform a write of any data value to it's allocated semaphore register. The write must be followed by a read to determine if it succeeded. The value zero will be returned if there was no success and the value one will be returned if the operation succeeded. To clear the semaphore another write of any data value must be done by the processor owning the semaphore.

# 3.9 Debugging Aids

Since access to signals within the internal processor is not possible, a two-fold strategy has developed for debugging the firmware. First of all it is expected that all software will be simulated prior to executed on the actual adapter. This allows full access to any portion of the Tigon as well as creates an environment where it is easy to test unusual conditions. Secondly *hooks* have been put into the Tigon to allow special host software to act as a debugger. This allows for the ability to do simple operations in a real-time environment. This host-based debugger need not access the adapter through the driver in the event that the driver is also being debugged.

The host has access to the internal processor's Program Counter and register file at all times. This allows the host to know from where code is being executed. Another register provides the ability for the host to stop as well as single-step the internal processor (see Section 9.5.1 "Miscellaneous Host Control"). Once the internal processor is stopped, then the host can even write to the Program Counter register in order to force execution to start at another location.

### 3.10 Reset

A hardware reset can be initiated by the PCI reset signal, the Misc. Host register, or the watchdog timer. All sources force the CPU to follow the same sequence of events. A reset does not alter the values of the register file or the internal scratch pad, but any subsequent ROM code will alter some of the locations in those memories.

If the revision of the Tigon contains more than one processor, than both will be reset at the same time. Only the processor with ROM code will start execution after the reset is completed.

# 3.11 Watchdog Timer

Each processor in the Tigon has its own watchdog timer feature to detect when the software is no longer operating normally. This feature can be enabled or disabled in the CPU State register and is disabled after a reset.

The watchdog state machine uses bit-19 of the Timer register to determine if the CPU needs to be reset. If the timer is set up to operate at the suggested 1 microsecond intervals, then bit-19 will toggle about every 0.5 second. The watchdog state machine looks for three transitions of the timer bit without having a write occurring to this Watchdog Clear register in order to reset the CPU. The 3 transitions ensures that reset would occur between 1 - 1.5 seconds after the last Watchdog Clear write. The data value written to the Watchdog Clear register is irrelevant.

If a Tigon revision which has more than one processor is being used, then it should be noted that either processor's watchdog timer expiring, will cause both processors to be reset. A watchdog reset does not affect the operation of any portion of the Tigon outside of the processors.

If software wishes to determine if the CPU was reset by the watchdog timer, then a bit not present in the CPU register region which normally would be preset/cleared by a full reset can be used. This bit can be set to the non-reset value during initialization. If prior to initialization this bit is in the non-reset state, then only the CPU must have been restarted. A more complex algorithm may be needed depending on if there are other reasons the software may have been restarted.

### 3.12 ROM Code

The Tigon contains several hundred instructions of on-chip code in read-only memory (ROM) that the processor<sup>1</sup> executes when it first comes out of reset. The purpose of this code is to locate, load, verify, and run a program from external storage, thus providing the ability for the Tigon to boot without the aid of another processor or external logic. Bootload code can be found in either serial EEPROM, or a parallel storage device mapped into the Tigon's flash memory space. Priority is given to the serial EEPROM. The flash memory space is only checked if attempts to read from serial EEPROM fail.

As the ROM code executes, the top 4 bytes of internal scratchpad is used to indicate its progress<sup>2</sup>. This provides a means of determining the progress of the ROM from an external host. The ROM progress code is located at address 0x000C03FFC (in the local processor's address space) and the values that it takes are defined in Table 8.

| Progress Code | Description                                                  |  |  |  |

|---------------|--------------------------------------------------------------|--|--|--|

| 1             | ROM is attempting to read from serial EEPROM.                |  |  |  |

| 2             | ROM is attempting to read from flash.                        |  |  |  |

| 3             | ROM found neither serial nor parallel device.                |  |  |  |

| 4             | CRC of bootload structure failed.                            |  |  |  |

| 5             | ROM is loading code (from either serial or parallel device). |  |  |  |

| 6             | ROM finished ok, ROM_FAIL bit has been cleared.              |  |  |  |

| Table 8. | ROM | Progress | Code |

|----------|-----|----------|------|

|          |     | 1.09.000 |      |

When ROM begins to execute, it first attempts to read the magic value from serial EEPROM offset x10. If successful it reads the next four 32-bit words and checks the CRC. If the CRC passes, ROM loads code from serial EEPROM into SRAM and runs it, clearing the ROM fail bit. If any errors happen during the loading of code, the ROM halts. If either the CRC at offset x20 fails or the magic value is not found, the ROM code switches to try and load code from parallel space. Here the same procedure is repeated. If the magic value is not found or the CRC fails or an error happens while loading code, the ROM code halts.

Version 4 and earlier of the Tigon had a ROM\_FAIL bit in the CPU state register that was set by hardware during reset and cleared by ROM after loading code. Version 5 of the Tigon ASIC provides the same functionality as well as the ROM progress feature for backward compatibility.

<sup>&</sup>lt;sup>1</sup>Starting with Tigon revision 5, only CPU A can execute from ROM. <sup>2</sup>First implemented in Tigon revision 5.

On PCI bus-based systems, it may be desired to program PCI registers like the PCI device and vendor ID registers before the PCI BIOS accesses the Tigon. In this case the process described above can be used to load a short program into the Tigon's internal SRAM. This code would perform any time-critical setup and then load and run another program containing diagnostics or more boot code. This method of staged bootstrapping can also be used to load code that configures other parts of the Tigon such as the speed that flash is accessed or the type and configuration of external SRAM memory.

### 3.13 Bootload Data Structure

A serial EEPROM or parallel storage device is bootload-able if it adheres to the following structure. Byte ordering is big-endian. Each field shown below is 32-bits and all other offsets are don't care. Notice the first 16 bytes were skipped in order to avoid any potential overlap with pre-defined addresses within flash memory components.

| Logical Byte Offset | 32-bit Value                                                                                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0x10                | Magic value of 0x6699AA55.                                                                                                                   |

| 0x14                | Location in Tigon's address space to place code (int. or ext. SRAM).                                                                         |

| 0x18                | Code length in 32-bit words.                                                                                                                 |

| 0x1C                | Logical byte offset within device where 1st byte of code is located.                                                                         |

| 0x20                | 32-bit CRC, calculated for addresses $0x10-0x23$ (inclusive) for a total of 20 bytes. Make sure CRC is stored with big-endian byte ordering. |

Table 9. Bootload Data Structure

# 3.14 Accessing Serial EEPROM

Serial EEPROM, along with any I<sup>2</sup>C compliant device, may be connected to the Tigon using two pins; a data pin and a clock pin. These pins are controlled by bits in the Misc. Local register. There is no hardware support for accessing serial devices on these pins. The Tigon ROM can access one serial EEPROM device of up to 64K bytes of memory.

# 3.15 Accessing Flash

The Tigon supports an 8-bit wide parallel device such as an EEPROM or flash. If present, this device is mapped into the Tigon's Flash memory space and is connected to the most significant byte (bits 63-56) of the local memory bus. Because the parallel storage device is mapped into a single byte-lane on the Tigon's 64-bit memory bus, consecutive byte addresses in the parallel device exist eight bytes apart in the Tigon's memory space. As done in the ROM, software must take this into account when accessing this space. If a wider device is used, ROM will not take advantage of the additional width, though subsequent software may choose to do so.

Access timing for the flash memory space is programmable but defaults to a very slow timing which can accommodate a device with a 180ns or faster access time. For more details on altering the speed of accesses to the flash memory region see the Fast\_Flash bit in Section 9.5.2 "Miscellaneous Local Control" register and, starting in Tigon revision 5, the flash fields in Section 9.7.12 "CPU Priority" register.

Writes to the flash memory region are ignored unless the Enable\_Flash\_Writes bit has been set in the Misc. Local register. This is done to help prevent inadvertent writes to non-volatile memory by the host or local processor.

The Tigon PCI/Ethernet Controller contains a Main Event register which assists the internal processor in determining what task to perform next. Both hardware and software events are indicated in this event register. The processor's main loop is to wait for an event and then deal with them in a priority order. Two special instructions were created to allow the processor to priority encode the event register and use the most significant (highest priority) bit set to index into an event handing jump table. These instructions are the PRIO and JOFF instructions.

For Tigon revisions which contain two processors, there are two Main Event registers, one for each processor. There are common hardware events, but each has its own software events. There are also interprocessor events to facilitate communication between the two processors.

Intermixed with the hardware event bits are bits which are not preset by hardware. These additional bits are entirely managed by firmware as a means of indicating additional events which need processing. These bits are spread out throughout the event register as a means of allowing firmware to utilize various priority levels for these firmware events.

Event bit positions which are to be ignored can be masked off by the firmware. The priority encode instruction provides a means to specify a mask register which gets ANDed with the register which is to be priority encoded. In this manner firmware can manage a mask register.

The layout of the Main Event register can be found in Section 9.5.8, "Main Event A/B."

### 4.1 Timer Event

One of the events worth special attention is the timer function. This is a 32-bit counter which advances every 1-128 local clock cycles depending on the value of a pre-scaler. If the timer is set up to increment every microsecond, then this counter in effect rolls over every about every 71 minutes. A queue of time-based functions is maintained by the processor with the top entry in the queue managed by hardware. The processor can schedule future events by taking the current timer value and adding the number of "microseconds" at which it would like to receive an event. This value should be written to the timer reference register so that an event can be generated when the timer is equal to the timer reference. The processor makes heavy use of this event to provide time-outs, interrupts, and any other function in which it would be bad to create firmware spin loops.

### 4.2 Mailbox Events

This event indicates that a mailbox location was written to using the target interface on the PCI bus. Since there are 32 possible mailbox locations, a separate Mailbox Event register was created which feeds into the main Event register as a single bit. Any bit set in the Mailbox Event register will cause the corresponding indication in the Event register. If firmware wished to mask off certain mailbox events, then this masking function need by done by the firmware prior to using the mailbox event register. Mailbox events are cleared by setting a "1" in each bit position to be cleared as a write is performed to the Mailbox Event register.

To support multiple processors, the 32 mailboxes can be split into two groups of 16 events. Each group feeds a different Main Event register. This allows each processor to manage its own private mailbox events. This option is further defined in Section 9.5.3, "Miscellaneous Configuration."

## 4.3 UART Events

The UART which is built into the Tigon generates events as a means to indicate that a byte has been transferred. The UART operates in a full-duplex capacity, so as soon as the event is generated another byte can begin transferring. There is an event for byte transmission, byte reception and the receive byte FIFO has overrun causing the loss of at least one byte. These events are defined in Section 9.5.2, "Miscellaneous Local Control" register.

# 4.4 PCI Interrupt Event

The PCI Interrupt Event is a hardware maskable event which allows the Tigon to respond to the assertion of the PCI Interrupt pin. This event would not be used when the Tigon is used as a normal network interface card, but rather in custom applications. If enabled, this event remains active until the input pin gets deasserted. The enable bit appears in Section 9.5.3, "Miscellaneous Configuration" register, while the event appears along with the UART events in Section 9.5.2, "Miscellaneous Local Control" register.

# 4.5 DMA Completed Events

There are two events associated with DMA completion. One for the read DMA channel and one for the write DMA channel. These events indicate that a host read or write DMA has completed. These events are always asserted as long as the respective DMA channel is not active. If the firmware chooses to directly control the starting of the DMA channels, then it would reference these events. Otherwise the Assist logic should be activated to control the starting of the DMA channels through the use of DMA descriptors in memory. With the Assist logic enabled, these events should be masked off by firmware.

The DMA completed events only indicates DMA operations which have completed successfully. See the respective attention events for the reporting of DMA errors.

# 4.6 Assist Completed Events

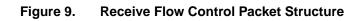

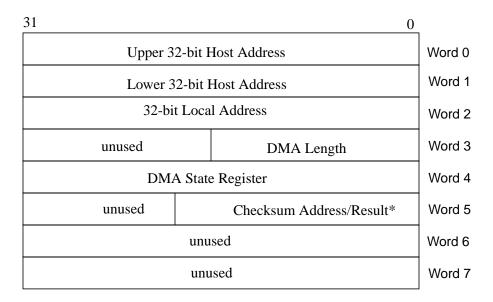

There are four event associated with Assist Completion. A high and low priority for each of the read DMA and write DMA channels. These events are only allowed to be generated if the Assist state machine has been enabled to control the DMA channels based on DMA descriptors in local memory. The assist logic supports 16 DMA descriptors in a circular ring fashion in local memory for each of the four events. A producer, consumer, and reference registers are used to manage each ring. At any time the reference register is pointing to a descriptor which has been completed by the DMA channel as indicated by the producer advancing past the descriptor, but not yet acknowledged by the firmware as indicated by the consumer not yet reaching the descriptor (i.e. reference not between the producer and consumer, nor equal to consumer), then the respective event is generated. The high priority rings are always serviced prior to the low priority rings.

## 4.7 DMA Read Attention

This event is used to indicate than the DMA stopped due to an error. This event is not present if a host read DMA is active. The exact cause of the error can be determined by reading the DMA Read State register. This event has a higher priority than the DMA Read Completed so that firmware can chose to use this event as a stopped due to an error indication. The conditions for generating this event can be found in the upper byte of the register defined in Section 9.6.3, "DMA Read State."

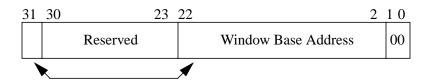

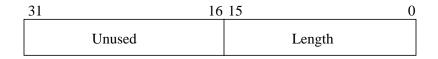

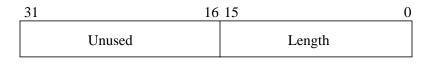

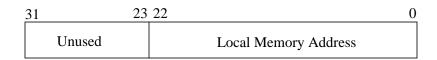

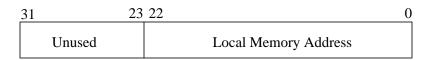

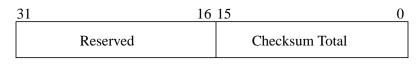

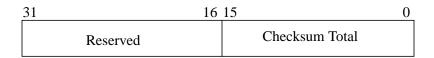

# 4.8 DMA Write Attention